1 Background on The Behavior of Bipolar and MOS Transistors and Inverters

at High Temperatures |

1 |

| 1.1 Introduction |

1 |

| 1.2 Background In High Temperature Electronics |

1 |

| 1.2.1 Cmos And BJT High Temperature Operation |

2 |

| 1.2.2 Latch-Up |

8 |

| 1.3 High Temperature Silicon Device Behavior, Summary |

10 |

| 2 Bipolar Junction Transistor At Elevated Temperatures |

15 |

| 2.1 Operation of The Bipolar Junction Transistor |

15 |

| 2.2 Model of The Bipolar Junction Transistor |

19 |

| 2.3 Temperature Dependent Parameters of The BJT |

22 |

| 2.4 Temperature Dependence of Current Gain (β) |

25 |

| 2.5 Temperature Dependence Of Bjt Inverter Circuit |

26 |

| References |

29 |

3 Computer Simulations of Bipolar Junction Transistor and Experimental

Validation |

31 |

| 3.1 Simulations at Elevated Temperatures |

31 |

| 3.1.2 Pspice Simulations for High Temperature Electronics |

33 |

| 3.2 Experimental Analysis of BJT Behavior |

35 |

| 3.2.1 Beta Versus Temperature |

35 |

| 3.3 Bjt Inverter Voltage Transfer Characteristic at Elevated Temperatures |

37 |

| 3.4 Electrical Measurements To Obtain BJT Thermal Resistance |

39 |

| 3.5 Observations of Bipolar Junction Transistor Behavior at High Temperatures |

41 |

| 3.5.1 Beta Versus Temperature Dependence |

41 |

| 3.6 Bipolar Transistor Voltage Transfer Characteristics (VTC) |

42 |

| References |

45 |

4 Introduction To The High Temperature Behavior of The Metal Oxide Silicon

Field Effect Transistor |

47 |

| 4.1 Physical Operation of a MOSFET |

47 |

| 4.2 Temperature Dependent Parameters |

50 |

| 4.3 N-MOS Inverter Voltage Transfer Characteristic ( VTC ) |

51 |

| 4.4 Cmos Inverter Voltage Transfer Characteristic |

53 |

| 4.5 Propagation Delay of The Cmos Inverter |

58 |

| 4.6 Simulations of The NMOS Inverter VTC |

61 |

| 4.6.1 Computer Simulations |

61 |

| 4.6.2 Pspice Simulation |

62 |

| 4.7 Computer Simulations of The Cmos Inverter VTC |

63 |

| 4.7.1 Program Simulation |

63 |

| 4.7.2 Pspice Simulation |

64 |

| 4.7.3 Propagation Delay of The CMOS Inverter |

65 |

| 4.8 Experimental Analysis of The NMOS Inverter |

67 |

| 4.9 Observations of MOSFET Behavior at High Temperatures |

69 |

| 4.9.1 NMOS Inverter |

69 |

| 4.9.2 CMOS Inverter |

70 |

| 4.10 Conclusions |

71 |

| 4.11 Recommendations for Further Work |

72 |

| References |

73 |

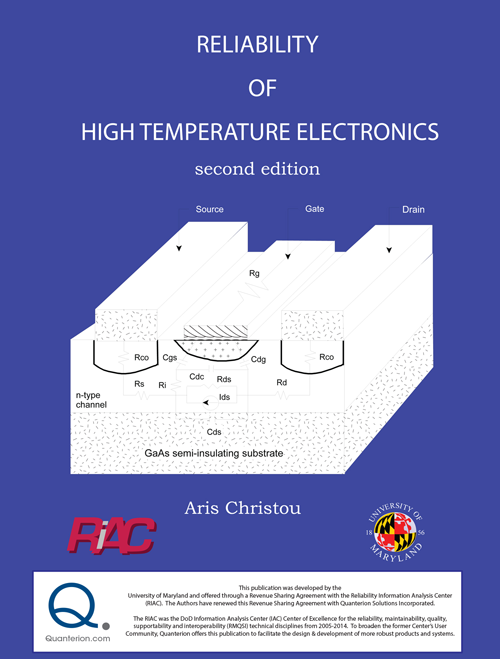

5 High Temperature Modeling and Thermal Characteristics of GaAs

MESFETs |

75 |

| 5.1 Introduction |

75 |

| 5.2 State-Of-The-Art for Modeling High Temperature Characteristics |

77 |

| 5.3 Chapter Outline and Objectives |

78 |

| 5.4 Physical Properties of MESFETs at Elevated Temperatures |

79 |

| 5.4.1 Gallium Arsenide |

79 |

| 5.4.2 Energy Gaps and Intrinsic Carrier Densities |

79 |

| 5.5 Carrier Mobilities and Saturation Velocity |

84 |

| 5.6 Modeling of MESFETs |

88 |

| 5.6.1 Introduction |

88 |

| 5.6.2 Principles of MESFET Operation |

89 |

| 5.6.3 Linear Region of MESFET Characteristics |

90 |

| 5.6.4 Saturation Region Model |

91 |

| 5.7 Empirical MESFET Model |

92 |

| 5.8 Temperature Related Properties of GaAs MESFET |

96 |

| References |

101 |

6 Computer Simulation and Electrical Measurements of The MESFET

Temperature Dependence |

103 |

| 6.1 Introduction To The Simulation of Temperature Dependence |

103 |

| 6.2 Simulation Results for The MESFET |

105 |

6.2.1 Comparison of MESFET Simulation: Hyperbolic and

Quadratic Model |

105 |

| 6.2.2 Simulation Results of The ZTC Bias Point of GaAs MESFET |

114 |

| 6.2.3 Temperature Dependent Characteristics of The GaAs MESFET |

126 |

| 6.2.4 Electrical Measurement at Elevated Temperatures |

135 |

6.3 Thermal Measurements of GaAs Devices Using IR Microscopy Techniques

|

138 |

| 6.3.1 Operation Principle of The IR Microscope |

138 |

| 6.3.2 IR Microscopy Measurement Results |

140 |

| 6.4 Finite Element Analysis of Heat Transfer In The GaAs MESFET |

142 |

| 6.4.1 General Mathematical Assumptions and Model |

142 |

| 6.4.2 Simulation Results and Comparison with Measurements |

143 |

| 6.5 Summary and Conclusions |

146 |

| 7 Temperature Effects of Heterostructure Transistors and Circuits |

151 |

| 7.1 Introduction |

151 |

| 7.2 Physical Properties of AlGaAs/GaAs HFET |

152 |

| 7.2.1 AlGaAs/GaAs HFET Device Structures |

152 |

| 7.2.2 Principles of HFET Operation |

153 |

| 7.2.3 Modulation Doping |

154 |

| 7.3 Aim-Spice HFET Model |

155 |

| 7.3.1 HFET Model for Aim-Spice Input File |

156 |

| 7.3.2 Current-Voltage Model Used By Aim-Spice |

156 |

| 7.4 Current-Voltage Characteristics of AlGaAs/GaAs Hfet |

159 |

| 7.4.1 Intrinsic Current-Voltage Characteristics |

159 |

| 7.4.2 Extrinsic Current-Voltage Characteristics |

161 |

| 7.5 Temperature Dependent Characteristics of HFET |

164 |

| 7.5.1 Energy Gap And Intrinsic Carrier Concentration |

164 |

| 7.5.2 Threshold Voltage and Dielectric Permittivity |

168 |

| 7.5.3 Saturation Velocity and Electron Mobility |

169 |

| 7.5.4 Temperature Dependence of Current-Voltage Characteristics |

174 |

| References |

179 |

| 8 High Temperature Behavior of The HFET Inverter |

181 |

| 8.1 Introduction |

181 |

| 8.2 Inverter Circuits |

181 |

| 8.2.1 Basic Inverter |

181 |

| 8.2.2 Direct-Coupled Fet Logic (DCFL) Inverter |

183 |

| 8.2.3 Buffered Fet Logic (BFL) Inverter |

183 |

| 8.3 Failure Mechanisms of AlGaAs/GaAs HFET at Elevated Temperatures |

185 |

| 8.3.1 Interdiffusion |

185 |

| 8.4 Kink Effect |

190 |

| 8.5 Ohmic Contact Resistance Increase |

191 |

| 8.6 Thermal Runaway Effect |

192 |

| 8.7 Gate Degradation |

192 |

| 8.8 Conclusions |

193 |

| References |

197 |

| 9 Elevated Temperature Power Semiconductor Devices |

199 |

| 9.1 Introduction |

199 |

| 9.2 Power Semiconductor Device Materials |

200 |

| 9.3 Power Semiconductor Device Reliability |

201 |

| 9.3.1 Device Failure Modes at Elevated Temperatures |

202 |

| 9.4 Power Transistor Packaging |

204 |

| 9.4.1 Materials for Power Transistor Packaging |

205 |

| 9.5 Power Package Failure Modes and Reliability |

209 |

| 9.5.1 Thermomechanical Stress |

209 |

| 9.5.2 Moisture Related Failure Mechanisms |

211 |

| 9.5.3 Thermal Fatigue |

211 |

| 9.6 Heat Dissipation In Power Transistors |

212 |

| 9.7 Power Dissipation In Power Transistors |

213 |

| 9.7.1 Thermal Management |

213 |

| 9.8 Simulation of Elevated Temperature Effects |

213 |

| 9.8.1 Process Simulation |

214 |

| 9.8.2 Numerical Device Simulation |

215 |

| 9.8.3 Device Simulation |

215 |

| 9.8.4 Package Simulation |

217 |

| 9.9 Tests and Measurements |

217 |

9.9.1 Electrothermal Models For Measurement of Power Device

Parameters |

218 |

| 9.9.2 Thermal Impedance Measurements |

219 |

| References |

221 |

| 10 Design Optimization of High Temperature Electronic Packaging |

225 |

| 10.1 Introduction |

225 |

| 10.2 Design Constraints Imposed by Temperatures |

226 |

| 10.2.1 Die Information |

226 |

| 10.2.2 Mounting Platform Technology Information |

227 |

| 10.3 High Temperature Packaging Design Goals |

227 |

| 10.3.1 Performance |

227 |

| 10.3.2 Reliability |

228 |

| 10.4 Applying The High Temperature Design Guidelines |

228 |

| 10.4.1 Die to Lead Interconnect |

230 |

| 10.4.2 Lead |

231 |

| 10.4.3 Case |

231 |

| 10.4.4 Die and Substrate Attach |

233 |

| 10.4.5 Lead Seals |

233 |

| 10.4.6 Lid and Lid Seal |

233 |

| 10.5 High Temperature Electronic Package |

234 |

| 11 Introduction to The High Temperature Reliability Issues of MMICs |

245 |

| 11.1 Background |

245 |

| 11.2 State-Of-The-Art of MMIC High Temperature Behavior |

247 |

| 11.3 Chapter Outline |

249 |

| References |

253 |

| 12 MMICs and Monte Carlo Technique |

257 |

| 12.1 Monolithic Microwave Integrated Circuits for High Temperatures |

257 |

| 12.1.1 MMIC Status |

257 |

| 12.1.2 MMIC Performance |

258 |

| 12.1.3 MMIC Applications |

259 |

| 12.2 Monte Carlo Techniques for Design and High Temperature Prediction |

260 |

| 12.2.1 Introduction to Monte Carlo Methods |

260 |

12.2.2 High Temperature Reliability Simulations by Monte Carlo

Techniques |

262 |

| References |

265 |

| 13 MMIC High Temperature Reliability |

269 |

| 13.1 Introduction |

269 |

| 13.2 MMIC High Temperature Reliability Mathematics |

271 |

| 13.3 Investigations of MMIC Reliability |

277 |

| 13.4 Concerns of High Temperature MMIC Reliability |

279 |

| References |

283 |

| 14 MMIC High Temperature Testing Methodology and Analysis |

287 |

| 14.1 Introduction to Arrhenius Model |

287 |

| 14.2 Accelerated Life Tests |

291 |

| 14.2.1 Introduction |

291 |

| References |

295 |

| 15 MMIC Circuit High Temperature Analysis |

297 |

| 15.1 MMIC Circuit Modeling for High Temperature Design |

297 |

| 15.1.1 Introduction |

297 |

| 15.1.2 Operation Principles of MESFET |

298 |

| 15.1.3 Theoretical I-V Characteristics of GaAs MESFET |

302 |

| 15.1.4 GaAs MESFET Spice3 Model |

305 |

| 15.2 MMIC Spice Circuit Analysis |

311 |

| 15.2.1 Spice Analysis For MMICs |

311 |

| 15.2.1.1 Transimpedance Amplifier (TIA) |

311 |

| 15.2.1.2 EG-6101 Low-Noise Amplifier |

314 |

| 15.3 The Methodology to Determine the Correlation Matrix of MMICs |

314 |

| 15.3.1 Introduction to Correlation Mathematics |

314 |

| 15.3.2 Statistical Model for the Correlation between MMIC Devices |

316 |

| 15.3.3 The Methodology to Estimate the Correlation of MMICs |

318 |

| References |

321 |

| 16 Monte Carlo High Temperature Reliability Model for MMICs |

325 |

| 16.1 Introduction |

325 |

| 16.2 The Methodology to Estimate MMIC High Temperature Performance |

325 |

| 16.2.1 The Joint Probability Method Via Monte Carlo Simulation |

325 |

| 16.2.2 The Non-Markovian Method Via Monte Carlo Simulation |

327 |

| 16.2.3 The MMIC Monte Carlo Technique |

328 |

| 16.3 MMIC Circuit Reliability Model |

328 |

| 16.3.1 The Given Conditions For MMIC Reliability Model |

328 |

| 16.3.2 Procedures to Model MMIC Reliability |

331 |

| 16.3.3 Validation of MMIC High Temperature Model |

338 |

| 16.3.3.1 EG-6101 LNA and TIA High Temperature Analysis |

338 |

16.3.3.2 EG-6010 LNA and EG-6203 Power Amplifier Reliability

Analysis |

341 |

| 16.3.3.3 Simulation Results |

341 |

| References |

345 |

| A1 Software and Manual, User’s Guide |

347 |

| A1-1 Introduction |

347 |

| A1-2 How to Run Device2 |

347 |

| A1-2-1 Detailed Description for F1 |

348 |

| A1-3 Detailed Description for Function Key 2 |

349 |

| A1-4 Description for F3 |

351 |

| A1-5 Description for F4 |

352 |

| A1-6 Description for F5 and F6 |

354 |

| A1-7 Description for F7 |

355 |

| A1-8 Description for F8 |

356 |

| A2 Program for Calculation of The Current-Voltage Characteristics of The HFET |

357 |

| B Program for Calculation of The Temperature Dependent Characteristicsof The HFET |

359 |

| B-1 For Calculation of The Temperature Dependence of Energy Gap for GaAs |

359 |

B-2 For Calculation of The Temperature Dependence of Intrinsic Carrier

Concentration of GaAs |

360 |

| B-3 For Calculation of The Temperature Dependence of Saturation Velocity |

361 |

B-4 For Calculation of The Temperature Dependence of Electron Mobility at

Three Different Concentration |

362 |

B-5 For Calculation of The Temperature Dependence of Current-Voltage

Characteristics |

364 |

B-6 For Calculation of The Temperature Dependence of Drain-To-Source

Saturation Current |

367 |

B-7 For Calculation of The Temperature Dependence of Extrinsic Drain Saturation

Voltage |

369 |

| C Aim-Spice Simulation Circuits and Input Files |

371 |

| C-1 Simulation Circuit For Current-Voltage Characteristics |

371 |

| C-2 Input File for I-V Characteristics (Ids Versus Vds) (for Vg = 0.3v only) |

371 |

| C-3 Input File for I-V Characteristics (Ids Versus Vg) (for Vdd = 1v only) |

371 |

| C-4 Direct-Coupled FET Logic (DCFL) Inverter Circuit |

372 |

| C-5 Input File for Direct-Coupled Fet Logic (DCFL) Inverter |

372 |

| C-6 Buffered FET Logic (BFL) Inverter Circuit |

373 |

| C-7 Input File for Buffered FET Logic (BFL) Inverter |

373 |